布局布线

电路板布局、布线的的抗ESD设计规则

一、概述:

静电释放(ESD)是我们每一个产品设计工程师需要考虑的一个相当重要的问题。大多数电子设备都 处于一个充满ESD的环境之中,ESD可能来自人体、家具甚至设备本身(内部)。电子设备完全遭受ESD损毁比较少见,然而ESD干扰却很常见,它会导致设备锁死、复位、数据丢失和不可靠。其结果可能是:在寒冷干燥的冬季里,电子设备经常出现故障现象,但是维修时又显示正常。

要防止ESD,首先必须知道ESD是什么及ESD进入电子设备的过程。一个充电的导体接近另一个导体时,就可能发生ESD。首先,在2个导体之间会建立一个很强的电场,产生由电场引起的击穿。当2个导体之间的电压超过它们之间空气和绝缘介质的

击穿电压时,就会产生电弧。在0.7ns~10ns的时间里,电弧电流会达到几十A,有时甚至会超过100A。电弧将一直维持,直到2个导体接触短路或者电流低到不能维持电弧为止。

1.1 ESD的产生取决于物体的起始电压、电阻、电感和寄生电容:

● 可能产生电弧的实例有人体、带电器件和机器。

● 可能产生尖峰电弧的实例有手或金属物体。

● 可能产生同极性或极性变化的多个电弧的实例有家具等。

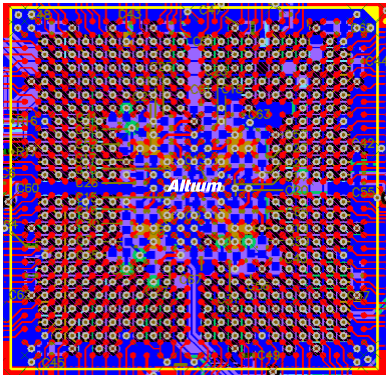

PCB设计中BGA器件如何走线、布线?

SMT技术顺应了智能电子产品小型化,轻型化的发展潮流,为实现电子产品的轻、薄、短、小打下了基础。SMT技术在90年代也走向成熟的阶段。但随着电子产品向便携式/小型化、网络化方向的迅速发展,对电子组装技术提出了更高的要求,其中BGA(Ball Grid Array 球栅阵列封装)就是一项已经进入实用化阶段的高密度组装技术。

BGA技术的研究始于60年代,最早被美国IBM公司采用,但一直到90年代初,BGA 才真正进入实用化的阶段。由于之前流行的类似QFP封装的高密管脚器件,其精细间距的局限性在于细引线易弯曲、质脆而易断,对于引线间的共平面度和贴装精度的要求很高。 BGA技术采用的是一种全新的设计思维方式,它采用将圆型或者柱状点隐藏在封装下面的结构,引线间距大、引线长度短。这样, BGA就消除了精细间距器件中由于引线问题而引起的共平面度和翘曲的缺陷。

BGA是PCB上常用的元器件,通常80﹪的高频信号及特殊信号将会由这类型的封装Footprint内拉出。因此,如何处理BGA 器件的走线,对重要信号会有很大的影响。