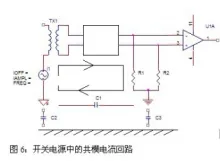

电源噪声滤波器的基本原理与应用方法

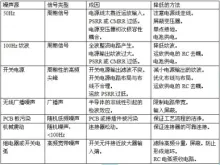

随着现代科学技术的飞速发展,电子、电力电子、电气设备应用越来越广泛,它们在运行中产生的高密度、宽频谱的电磁信号充满整个空间,形成复杂的电磁环境。复杂的电磁环境要求电子设备及电源具有更高的电磁兼容性。于是抑制电磁干扰的技术也越来越受到重视。接地、屏蔽和滤波是抑制电磁干扰的三大措施,下面主要介绍在电源中使用的EMI滤波器及其基本原理和正确应用方法。

<strong>电源设备中噪声滤波器的作用</strong>

电子设备的供电电源,如220V/50Hz交流电网或115V/400Hz交流发电机,都存在各式各样的EMI噪声,其中人为的EMI干扰源,如各种雷达、导航、通信等设备的无线电发射信号,会在电源线上和电子设备的连接电缆上感应出电磁干扰信号,电动旋转机械和点火系统,会在感性负载电路内产生瞬态过程和辐射噪声干扰;还有自然干扰源,比如雷电放电现象和宇宙中天电干扰噪声,前者的持续时间短但能量很大,后者的频率范围很宽。另外电子电路元器件本身工作时也会产生热噪声等。

这些电磁干扰噪声,通过辐射和传导耦合的方式,会影响在此环境中运行的各种电子设备的正常工作。

电源完整性设计干货之三——如何量化使用电容去掉电源噪声

对于已经知道了电容的具体特性和适用范围,以及去耦原理,那么就知道了去耦的具体方法了吗?不是的,下面我们将讲解一下,具体安装到电路板上之后的去耦原理以及具体如何防止电容的准则!

<strong>实际贴片上的电容的特性</strong>

上一节我们已经讲到电容的具体特性,但是等我们装配到电路板上之后电容的特性会保持和他之前的具体参数一致吗?

答案是否定的!

当电容具体安装到电路板上之后,还会引出额外的寄生参数,从而引起具体的谐振频率的偏移。充分理解电容的自谐振频率与安装谐振频率非常重要。在计算具体参数时,我们需要参考的数据时电容的安装自谐振频率。

电容在电路板上的安装通常包含一段从焊盘引脚拉出的一段引出线,两个或者更多的过孔,这些过孔,引出线会对电容残生哪些具体的影响呢?

假如,电容要对距离它2CM处的一个地方去耦,这是需要考虑几个部分呢?

1、受限电容自身存在的寄生电感,寄生电阻。

2、从电容达到需要去耦区域的路径上的焊盘、引出线、过孔。

3、从去耦区域到达电容地回路上的2CM长的电源及地平面。

这其中,过孔的寄生电感影响最大,其中过孔的半径越大,影响越小。如何计算呢?

电源完整性设计干货之二——电容是如何去掉电源噪声的来龙去脉

<strong>采用电容退藕是去掉电源噪声的主要办法</strong>

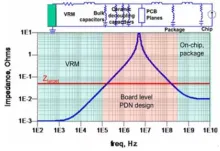

采用电容退藕的方式对提高瞬态电流响应及降低电源分配系统的阻抗都非常有效。

对于电容退藕,有些资料是从电荷存贮的角度去解释,而另外一些则是根据电源分配系统阻抗的角度去解释。这两种解释本质是一样的,只是看问题的角度不同而已。

<strong>电容去耦的两种解释如下:</strong>

1、从储能角度来解释

<center><img src="http://mouser.eetrend.com/files/2019-04/博客/100042638-67931-y1.jpg" alt=“去耦电容的工作原理” width="600"></center><center><i>去耦电容的工作原理</i></center>

电源完整性设计干货之一——电源噪声的前世今生

<strong>为什么要在意电源系统的信号完整性?</strong>

随着人工智能、物联网、VR/AR等技术的发展,相应的硬件技术也在日新月异。芯片的集成度也越来越高,内部的晶体管数量也越来越多。但是芯片的外片管脚是有限的,只能依靠内外部有限的供电管脚为内部数以亿计的晶体管供电。对于内部各个晶体管的操作通常由内核时钟及片内外设时钟来同步的,由于内部延时的原因,更晶体管的转换状态是不可能一致的。这就会导致电源噪声在系统内部相互传递。

除了影响芯片内部的正常工作状态,他还会对晶振、PLL、DLL的抖动特性及AD/DA转换电路的精度产生影响。

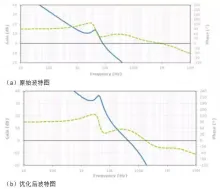

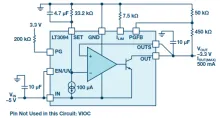

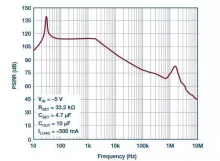

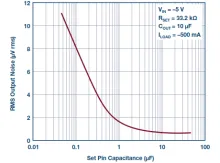

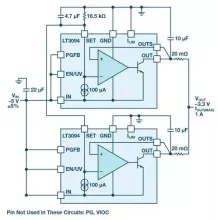

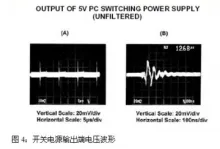

干货——对电源噪声特别敏感的滤波器设计

在一些对噪声特别敏感的电路中,如以太网物理层芯片的核心电源中,要求滤波电路不仅能衰减高频段噪声,而且能衰减低频段噪声。即要求此电源滤波电路作为一个全频段的噪声衰减器。这种设计方法长用于对噪声特别敏感的电源,如时钟的电源等。

<center><img src="http://mouser.eetrend.com/files/2019-04/博客/100018882-65335-l1.jpg" alt=“某以太网芯片的电源滤波电路” width="600"></center><center><i>某以太网芯片的电源滤波电路</i></center>

在此设计中LC电路能屡出高频段噪声,而本电路中的R则是作为一个噪声的全频段衰减器。当然了,在这些电路中电阻还有一个作用便是降低整个电源电路的品质因数Q。

Q定义为回路发生谐振时,存储能量与一周内消耗的能量比值。在一个有L、C、R组成的串联电路中,总阻抗为Z。