layout

技术博客 I 高速PCB Layout设计指南

随着工业上对新型自动化、消费者对无线设备、医疗和航空航天等领域对技术发展的需求日益增长,这些领域对PCB的需求也在不断升级。如果我们能紧跟需求,设计出更小且更复杂的电路板,便能实现PCB设计工具市场的增长。对于PCB设计人员而言,这意味着在设计方面所面临的新挑战比以往任何时候都多。

高速PCB的layout设计基于我们作为PCB设计人员已经掌握的技能。元器件的布局仍需要符合可制造性设计以及测试要求,而走线规划仍将采用行业公认的宽度和间距设计规则。然而,本文提出了我们都需要熟悉的一些更严格的高速电路相关要求和设计实践。我们将对其中部分进行详细说明,帮助您快速理解高速layout设计。

从原理图开始

DDR3 LAYOUT设计规则

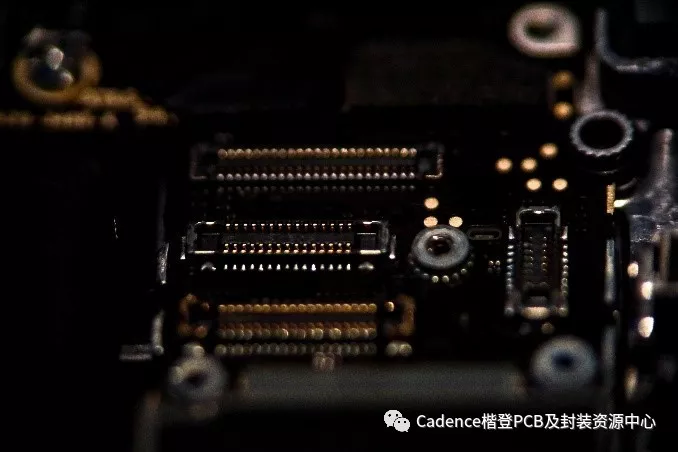

DDR3的设计有着严格等长要求,归结起来分为两类(以64位的DDR3为例): 数据 (DQ、DQS、DQM):组内等长,误差控制在20MIL以内,组间不需要考虑等长;地址、控制、时钟信号:地址、控制信号以时钟作参考,误差控制在100MIL以内,Address、Control与CLK归为一组,因为Address、Control是以CLK的下降沿触发的由DDR控制器输出,DDR颗粒由CLK的上升沿锁存Address、Control总线上的状态,所以需要严格控制CLK与Address/Command、Control之间的时序关系,确保DDR颗粒能够获得足够的建立和保持时间。

关注等长的目的就是为了等时,绕等长时需要注意以下几点:

1、确认芯片是否有Pin-delay,绕线时要确保Pin-delay开关已经打开;

2、同组信号走在同层,保证不会因换层影响实际的等时;同样的换层结构,换层前后的等长要匹配,即时等长;不同层的传播延时需要考虑,如走在表层与走在内层,其传播速度是不一样的,所以在走线的时候需要考虑,表层走线尽量短,让其差别尽量小(这也是为什么Intel的很多GUIDE上面要求,表层的走线长度不超过250MIL等要求的原因);

分页

- 页面 1

- 下一页