Vivado中如何避免信号被优化掉?

刚写了一段 Verilog代码,辛辛苦苦花了很长时间综合,在debug的过程中,却找不到需要debug的信号了,查看网表发现没有?这种情况是因为我们的某些中间信号被优化掉了。

FPGA时序约束实战篇之延迟约束

对于延迟约束,相信很多同学是不怎么用的,主要可能就是不熟悉这个约束,也有的是嫌麻烦,因为有时还要计算PCB上的走线延迟导致的时间差。而且不加延迟约束,Vivado也只是在Timing Report中提示warning,并不会导致时序错误,这也会让很多同学误以为这个约束可有可无。

Vivado调试小结:ILA debug中的数据也许并不可信

FPGA的调试是个很蛋疼的事,即便Vivado已经比ISE好用了很多,但调试起来依旧蛋疼。即便是同一个程序,FPGA每次重新综合、实现后结果都多多少少会有所不同。而且加入到ila中的数据会占用RAM资源,影响布局布线的结果。

FPGA中的上拉下拉电阻以及开漏推挽输出电路

什么是上拉/下拉电阻?有什么作用?又该怎么用?上拉电阻:将一个不确定的信号通过电阻连接到高电平(VCC),使该信号初始电平为高电平。下拉电阻:将一个不确定的信号通过电阻连接到低电平(GND),使该信号的初始电平为低电平。

Xilinx FPGA Configuration 技术小结

对于大部分人来说,至少入门时会用到的烧写方式就两种:① 通过JTAG直接将bitsteam 烧录到FPGA。② 在设计release以后,到产品上一般都是把配置文件通过IDE工具保存存在Nor Flash里。

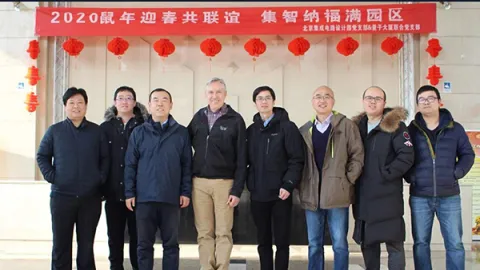

赛灵思副总裁到访北京深维科技,将进一步深化双方合作

近日,赛灵思VP(副总裁)Dan Gibbons一行到访北京深维科技,在CEO樊平及深维核心团队成员的陪同下,Dan Gibbons对深维科技进行了深入了解,双方在愉快的气氛中对之前的合作进行了梳理,并达成进一步深化合作意向,对于未来,双方都充满了紧密合作的期待。