思尔芯超大容量S8-100,简化并加速开芯院香山昆明湖16核RISC-V+NOC验证

S8-100搭载高性能AMD VP1902芯片,通过硬件升级显著提升了系统性能——单核等效1亿门容量,并具有丰富的资源和强大的可扩展性

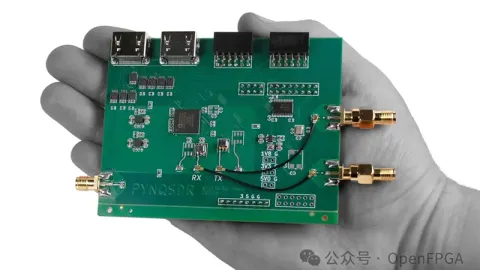

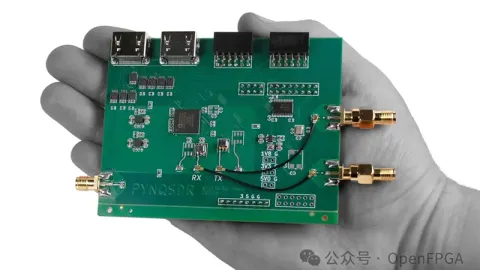

把 FPGA 搬进软件无线电:PynqSDR HAT 让通信实验不再 “烧钱”

今天要介绍的这款神器 ——PynqSDR HAT,正试图打破 “软件无线电 = 昂贵设备” 的刻板印象,让 FPGA 级别的通信实验变得触手可及。

使用 Xilinx FPGA 启用 AFE79xx SPI 的指南

本教程介绍了使用 Xilinx Vivado 和 Vitis 开发环境为德州仪器AFE79xx EVM 启用串行外设接口 (SPI) 和非时序关键型通用输出以及配套的 LMK 系列时钟芯片的过程

Advanced IO wizard异步模式

7nm Versal系列相对于16nm Ultrascale plus系列,IO做了升级,U+系列的HPIO在Versal升级为XPIO。Versal系列每一个XPIO bank包含54个IO管脚

嵌入式应用如何兼顾高性能与低功耗?Agilex™ 5 FPGA 和 SoC 给出答案

本文阐述了 Agilex™ 5 FPGA E 系列如何通过硬核内存控制器和增强型 I/O 组,简化时序收敛、降低动态和静态功耗,并高效实现低电压、高带宽的内存技术。

LSSD技术:高速LVDS接收相位自动调整方案

在当今高速数据传输领域,随着 LVDS 信号传输速率的不断提高,信号每位所占用的时间窗口不断减小,这使得采样时钟对信号的采样点在其有效区间采样的准确性降低

MATLAB 与 AMD Vitis™ HLS 协同工作,助力提升生产力

作为 MATLAB® R2025a 版的一部分,AMD Vitis™ HLS 开发人员现在可以使用强大而简化的流程,直接从 MATLAB(.m code)环境生成 Vitis HLS C++ 代码。