莱迪思将在2025上海车展上展示最新的FPGA方案

莱迪思将展示其最新的FPGA解决方案:基于ISO26262 ASIL-B认证的视频流和图标安全保护解决方案,旨在帮助智能汽车满足更高的功能安全合规性要求

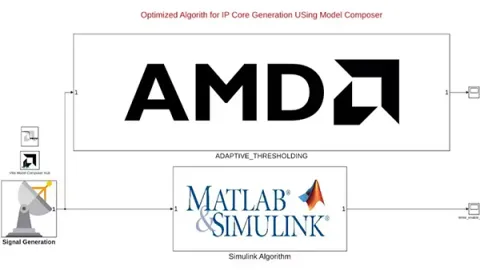

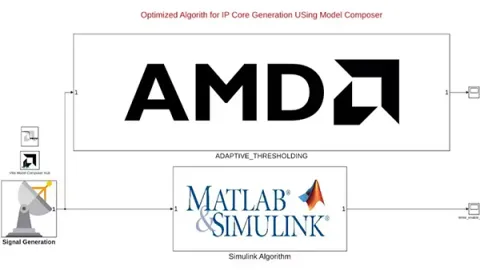

使用 Vitis Model Composer 生成 FPGA IP 核

今天的教程提供了创建自定义 IP 的分步指南,从算法开发到准备 IP 生成的模型,包括资源和时序分析,最后将其添加到 Vivado IP 目录。

移动产业处理器接口(MIPI)协议有哪些妙用?

<p><span style="text-wrap-mode: wrap;"><span style="text-wrap-mode: wrap;">未来汽车领域的发展愿景令人憧憬,其背后的驱动技术也因此备受关注。如今,传感器对于下一代汽车视觉与安全的发展至关重要</span></span></p>

合见工软发布国内首个HiPi标准的IP/VIP整体解决方案

首个HiPi (High Performance Chips Interconnection Alliance) 标准的IP/VIP整体解决方案拥有优秀的商用级高带宽、低延迟、低功耗、协议完备等特性

Microchip MCP16701:为 AI、工业及数据中心注入高效电源 “芯” 动力

MCP16701 集成了八个可并联的 1.5A 降压转换器、四个 300 mA 内部低压差稳压器(LDO)和一个用于驱动外部MOSFET的控制器