UltraScale/UltraScale+:异步模式的适用时机及其使用方式

在 UltraScale/UltraScale+ 中引入了 RXTX_BITSLICE。该原语用于捕获和接收 XPIO IOB。

重新定义机器人技术:高精度自主移动机器人

机器人基于莱迪思Avant™-E FPGA和英伟达公司的Jetson Orin,展示了实时决策和避障功能。它采用先进的传感器融合系统,集成了莱迪思视觉套件、激光雷达和雷达

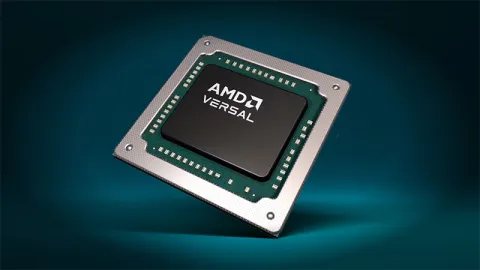

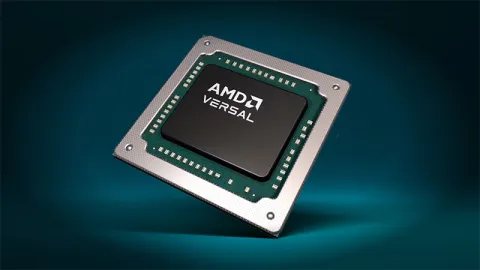

Versal:内置自校准 (BISC) 在异步模式下的工作原理及功能

本文提供有关 Versal 内置自校准 (BISC) 工作方式的详细信息。此外还详述了 Versal 的异步模式及其对 BISC 的影响。

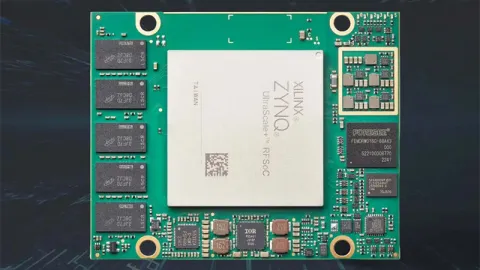

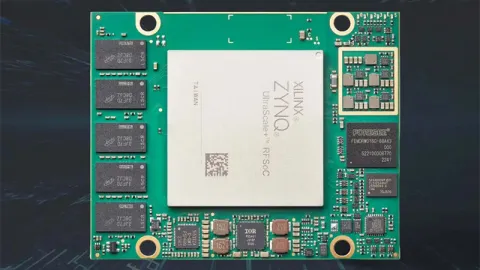

瑞苏盈科双Andromeda XRU50 RFSoC模块架构:构建先进实时频谱监测解决方案

瑞苏盈科推出的基于双Andromeda XRU50 RFSoC模块架构的实时频谱监测解决方案,以 “双芯协同” 为核心,实现了从信号采集到分析的全链路技术突破