QDMA Subsystem for PCI Express v5.0 产品指南

AMD QDMA Subsystem for PCI Express( PCIe® )旨在利用多队列的概念实现高性能 DMA,以搭配 PCI Express® Integrated Block 一起使用

Vitis HLS技术合集Vitis HLS(High-Level Synthesis)是 AMD 推出的面向 FPGA 的高层次综合工具,旨在通过 C、C++ 和 SystemC 等高级语言简化硬件设计流程。相较传统的 RTL 开发方式,Vitis HLS 极大提升了算法开发的效率与可重用性,加速了从原型设计到硬件部署的全过程。本合集系统梳理了 Vitis HLS 的核心原理、优化策略、指令用法、典型案例及与 Vivado/Vitis 平台的集成方法,帮助开发者快速掌握高性能硬件加速的设计技巧。无论你是算法工程师、嵌入式开发者,还是 FPGA 初学者,这套技术合集都将为你打开软硬协同开发的大门。

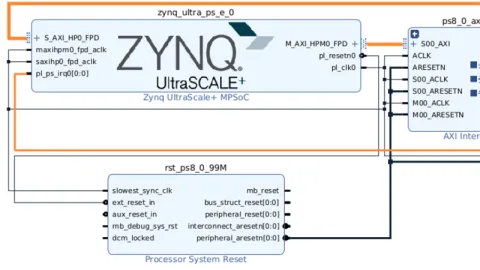

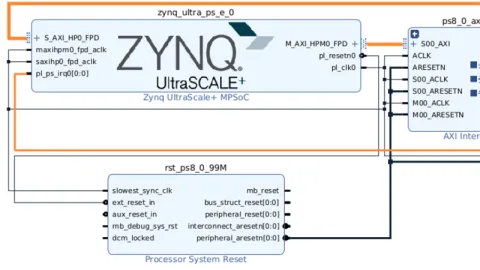

Vitis HLS 系列 1:Vivado IP 流程(Vitis 传统 IDE)

这篇博客旨在逐步演示如何使用 Vitis HLS 来创建一个 HLS IP,通过 AXI4 接口从存储器读取数据、执行简单的数学运算,然后将数据写回存储器

FPGA 大神 Adam Taylor 使用 ALINX VD100(AMD Versal系列)开发平台实现图像处理

这是一块基于 AMD Versal Edge AI 平台的开发板,功能特别强大,可以用来做图像处理、人工智能等各种高阶应用。

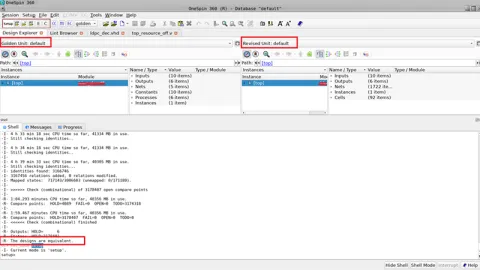

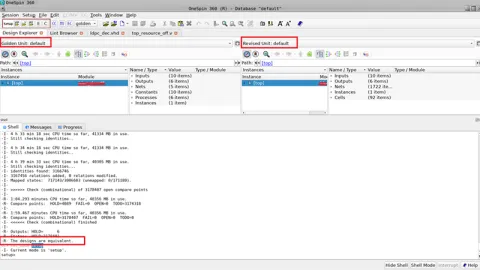

如何使用One Spin检查Vivado Synth的结果(以Vivado 2024.2为例)

本文讲述了如何使用 One Spin 检查 AMD Vivado™ Design Suite Synth 的结果(以 Vivado 2024.2 为例)。